Комплексное руководство по протоколу связи SPI

В этой статье мы рассмотрим детали протокола последовательного периферического интерфейса (SPI), сосредоточив внимание на его эффективных возможностях передачи данных и универсальных приложениях.SPI представляет собой высокоскоростный протокол синхронной связи, широко используемый в встроенных системах для подключения микроконтроллеров с различными периферийными устройствами.Благодаря своей конфигурации мастер-раба и четырьмя основными линиями-Miso, MOSI, SCLK и CS-SPI упрощает передачу данных, обеспечивая при этом синхронизацию между устройствами.Мы копаемся в основных принципах SPI, включая его эксплуатационную динамику, конфигурацию оборудования, диаграммы синхронизации и практические рекомендации по настройке.Если вы новичок в SPI или стремитесь усовершенствовать свое понимание, этот пост предоставит ценную информацию о максимизации своего потенциала в фактических приложениях.Каталог

Обзор протокола SPI

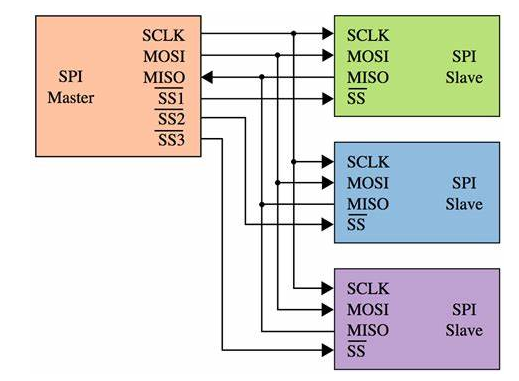

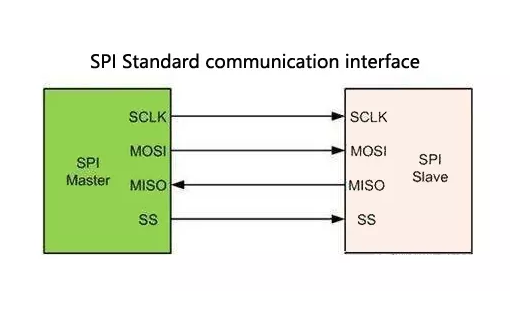

Последовательный периферийный интерфейс (SPI) использует 4-проводную систему, которая оптимизирует операции CPU за счет сокращения накладных расходов программного обеспечения.SPI, известный своей скоростью и эффективностью, является основным в таких устройствах, как AT91RM9200.В рамках мастер-рав, мастер управляет задачами, взаимодействуя с рабами через четыре необходимых провода: мисо (Мастер в рабстве), Моси (Магистр Рабов), SCLK (последовательные часы) и CS (Chip Select).Линия MISO направляет данные обратно в мастер, в то время как MOSI управляет исходящими данными.SCLK предоставляет сигналы часов от мастера, а CS облегчает управление активацией устройства.Простота SPI делает его в основном полезным для подключения нескольких устройств на одной шине, выполнения передачи данных последовательно и достижения синхронизации с помощью тактовых импульсов.Здесь мастер может приостановить связь, не влияя на надежность данных.В то время как SPI не хватает управления потоком, и функции подтверждения данных, его способность увеличивать периферические соединения через внешние декодеры компенсирует эти ограничения.

Конкретные случаи использования SPI

SPI строится вокруг отличительной настройки кольцевой шины с использованием таких деталей, как SS (CS), SCK, SDI и SDO для обмена данными регистрации.Например, 8-разрядная передача регистра использует края часов для управления движением данных и смены регистра.Инициализация в настройке мастер-рабов начинается с предварительно конфигурирующих буферов приемопередатчиков, иллюстрируя процесс связи.SPI Motorola превосходит в синхронной последовательной связи, используя MOSI, MISO и SCK для передовых задач с отправкой, гибкостью среди ролей в мастер-рабе и устойчивых функциональностей часов.Устройства должны синхронизировать тактовую фазу и полярность для согласованности связи.С возможностью связывать до 256 портов, SPI сосредоточен на подключении к точке и передаче данных на основе пакетов.

Пользовательская логическая формулировка

Проектирование адаптируемой пользовательской логики является динамической для приложений с многопортовыми структурами.В рамках конфигурации двойного порта независимые данные FIFO обрабатывают данные относительно адресов порта.Одновременно логический арбитраж контролирует проход данных к интерфейсу SPI4, приспосабливаясь к немедленным данным управления потоком и статусами FIFO.

SPI Операционная динамика

SPI спроектирован для надежной связи, включающей дискретные каналы для управления данными и потоком при передаче.Обширное подключение к порту разрешает передачу данных на основе пакетов, обеспечивая проверку точки-точки с помощью адресов пакетов, тем самым расширяя универсальность приложения.

Изучение диаграмм времени передачи данных

Интерфейсы SPI характеризуются четырьмя диаграммами синхронизации, условными в настройках CPOL и CPHA.CPOL определяет состояние холостого хода для SCK, тогда как CPHA обозначает край отбора проб.Эти конфигурации активны для обеспечения точности и синхронизации данных.

Синхронная серийная связь

Происвязана Motorola, SPI стоит как четырехпроводная, двунаправленная последовательная шина, разработанная для быстрой синхронной связи, связывая микроконтроллеры с периферийными устройствами, такими как EEPROMS, RTC и конвертеры A/D.Сеть SPI умело соединяет смешанные периферийные устройства, используя протоколы, которые обходят механизмы адреса для прямых, полнодуплексных обменов.Дополнительные линии, такие как int, могут улучшить реагирование системы.

Тонкости в конфигурации оборудования

Несмотря на мастерство SPI в взаимодействии с различными периферийными устройствами, индивидуальные сигналы для каждого устройства приводят к сложности по сравнению с более простыми системами, такими как I2C.Эта сложность является внутренним аспектом конфигурации аппаратного обеспечения SPI, включающей регистры смены для 8-битных передачи данных.Во время работы устройства надежно переключают биты через регистры, используя падение часов.

Оценка способности и практичности

Используя такие элементы, как Spiclk, Mosi, Miso и NSS, SPI Networks устанавливают роли мастер-рабов на основе состояний NSS PIN.Поддерживая единичные или многоотрастные среды, протокол адаптируется для контроля до 16 периферийных устройств.Несмотря на то, что ему не хватает методов контроля потока и подтверждения, структура протокола эффективно включает в себя различные настройки соединений и коммуникации.

Иллюстрации настройки и времени

Транзакции данных SPI регулируются прямыми правилами срока, под влиянием управления SCK.Например, шаблон регистра, такую как 10101010, отправляет битовые данные по сдвигам, управляемым часами, выделяя эксплуатационную простоту и динамику перехода данных на шине кольца.

Расширенное понимание производительности

Правильная синхронизация фазы тактовой частоты и полярности в мастер -и подчиненных устройствах используется для текущих транзакций данных.Такие параметры, как CPOL и CPHA, должны соответствовать устройствам в SPI-связанных системах для поддержания гармонии связи.

Практическая настройка совета

Корректировки конфигураций тактовых часов SPI должны учитывать требования часов подчиненного устройства, чтобы обеспечить точность данных во время циклов передачи.Распознавание краев сигналов во время передачи данных является серьезным для предотвращения несоответствий взаимосвязи.Руководства по продукту часто подробно описывают необходимые настройки, подчеркивая влияние точного выравнивания падения на точность передачи.

Основы общения SPI

По своей сути, последовательный периферический интерфейс (SPI) служит полномудуплексным, синхронным протоколом последовательной связи, требующим предварительного расположения взаимодействия.Эта функция отличает SPI, по своей природе выделяет синхронизированные обмены.Примечательным аспектом SPI является его зависимость от модели мастер-солевого, где мастер-устройство организует управление, генерируя сигналы тактовых сигналов и инициируя сеансы связи.Напротив, подчиненные устройства остаются остро настраиваемыми на эти сигналы, готовые участвовать при вызванном.

Механизм сотрудничества между Master и Slave Devices в SPI тщательно организован.Мастер несет исключительную ответственность за управление часами, обеспечивая устойчивый ритм для обмена данными.Этот надзор об оптимизации синхронизации, исключая непредсказуемость, часто присутствующую в асинхронных системах.Установив единую ссылку на время, оба устройства могут выполнять операции с точностью, практика, уточненная с помощью обширного опыта применения.Упорядоченный характер SPI обеспечивает эффективные возможности передачи данных, представляющие прямую альтернативу более сложным протоколам.

Структура SPI раскрывает определенные ограничения, особенно в настройках, которые подчеркивают легкость подключения и игры.Негибкий характер его протокола означает, что совместимость должна быть тщательно организована заранее.Устройства в рамках функции конфигурации SPI в рамках авторитета часов и предопределенных соглашений протоколов.Хотя это упрощает синхронизацию, она требует начальных усилий по настройке.Мрачное применение этих принципов продемонстрировало потенциал для облегчения расхождений в общении.Как отмечается в оценках сеанса, понимание структурной строгости SPI не только повышает практическое развертывание, но и повышает точность применения.

О нас

ALLELCO LIMITED

Прочитайте больше

Быстрое запрос

Пожалуйста, отправьте запрос, мы ответим немедленно.

Все о UDP: руководство по общению без соединения

на 2024/12/30

HD Technology: улучшение визуального превосходства

на 2024/12/30

Популярные посты

-

Комплексный набор инструкций: как они изменили вычисления?

на 8000/04/18 147758

-

Поспинка и функции USB-C

на 2000/04/18 111947

-

Использование примитивах Unified моделирования Xilinx: комплексное руководство по проектированию и моделированию FPGA

на 1600/04/18 111349

-

Напряжения источника питания в электронике: значение VCC, VDD, VEE, VSS и GND

на 0400/04/18 83722

-

Руководство по разъему RJ45: расписка, проводка, типы кабелей и использование

на 1970/01/1 79508

-

Конечное руководство по цветовым кодам проволоки в современных электрических системах

То, как наши электрические системы используют цвета, не только для внешнего вида.Каждый цвет провода теперь указывает на определенную функцию, что облегчает правильную идентификацию и обработку эле...на 1970/01/1 66916

-

Руководство по очистке клапана: функция, симптомы, тестирование и замена для оптимальной производительности двигателя

Клапан чистки является ключевой частью системы автомобиля, которая помогает поддерживать воздух в чистоте, управляя топливными парами, прежде чем они смогут сбежать в атмосферу.Это не только помога...на 1970/01/1 63075

-

Качество (Q) Фактор: уравнения и приложения

Коэффициент качества, или «Q», важен при проверке того, насколько хорошо индукторы и резонаторы работают в электронных системах, которые используют радиочастотные (RF).«Q» измеряет, насколько хорош...на 1970/01/1 63012

-

Достижение пиковой производительности с максимальной теоремой передачи мощности

Теорема максимальной передачи мощности объясняет, как энергия из источника, такого как батарея или генератор, течет к подключенной нагрузке.Он показывает точное условие, где нагрузка получает наибо...на 1970/01/1 54081

-

Спецификации батареи A23 и совместимость

Аккумулятор A23 представляет собой небольшую батарею в форме цилиндров с высоким напряжением.Также называется 23a, 23ae или Mn21, он работает на 12 вольт и намного выше, чем батареи AA или...на 1970/01/1 52143