CPLD объяснил: Руководство по программируемым логическим устройствам

В динамическом мире электронного дизайна сложные программируемые логические устройства (CPLDS) выделяются как универсальные инструменты, плавно смешивая адаптивность, точность и эффективность.Эти устройства революционизировали конструкцию схемы, внедрив программируемые макро -ячейки и доминирующую межсоединную матрицу, что позволяет создавать сложные логические функции с значительной надежностью.С самого начала в 1980 -х годах до их ключевой роли в современных отраслях, таких как сеть, автомобильная и аэрокосмическая промышленность, CPLD оказались необходимыми для вас, ищущих как гибкость, так и производительность.Эта статья входит в путешествие CPLD, их отличительные особенности, практические приложения и методологии программирования, которые делают их краеугольным камнем в дизайне цифровой логики.Каталог

Обзор CPLD

В доминировании сложных программируемых логических устройств (CPLDS) можно обнаружить сложный гобелен программируемых логических макро -ячейков, переплетенных через доминирующую межконтактную матрицу.Эти макролетки (MC) и входные/вывод (ввод/вывод) позволяют ловко проектировать цепи, настраивая структуры для уникальных функций.В отличие от устройств, которые озадачены их сложным временем соединения, CPLD используют неподвижные металлические провода.Эта характеристика дает им постоянное и предсказуемое поведение часов, что делает предсказания времени более надежными и точными.

Путешествие и использование

1970 -е годы ознаменовали появление программируемых логических устройств (PLDS), способствующих движению к программируемым макро -единицам.Этот сдвиг ввел достаточную гибкость дизайна, отличая их от статических цифровых цепей, хотя их утилита была первоначально ограничена более простыми цепями.Появление CPLDS в середине 1980-х годов произвело революцию в этом ландшафте, проложив путь к сложным конструкциям.С тех пор они вплетаются в ткань таких отраслей, как сеть, автомобильная электроника, обработка ЧПУ и аэрокосмические системы.Вы можете вспомнить о том, как CPLD упростили процессы, которые когда -то требовали тщательного ручного труда, отмечая замечательный скачок в эффективности.

Отличительные качества CPLD

CPLDs отличаются благодаря их адаптируемому программированию, обширной интеграции, быстрому развитию и широкой применимости, наряду с экономическими затратами на производство.Они обращаются к тем, кто имеет минимальный аппаратный опыт, служащий надежными и безопасными продуктами, которые не требуют исчерпывающего тестирования.В качестве свидетельства их мастерства в крупномасштабных конструкциях схемы, CPLD играют ключевую роль в разработке прототипа и обслуживают пробеги ниже 10 000 единиц, воплощая для вас полезную компетентность.Адепкость, с которой CPLD приспосабливаются к развивающимся требованиям проекта, часто приносит им оценку, подчеркивая их фактическую универсальность в динамических средах.

Методы применения

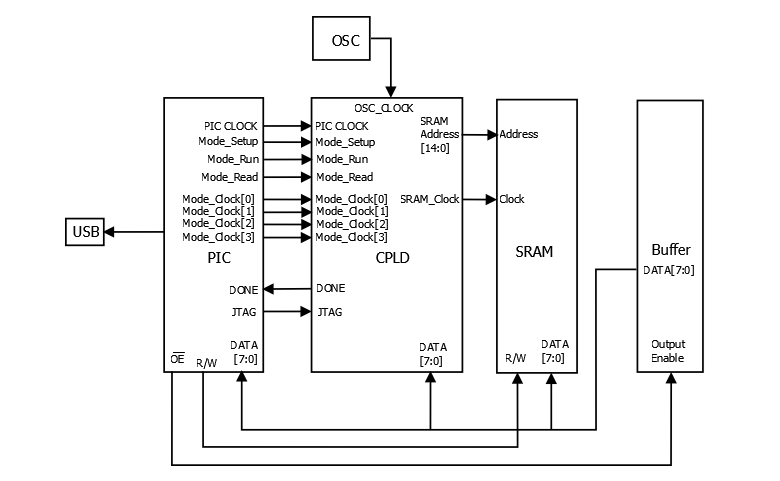

Эти интегрированные схемы позволяют вам разрабатывать логические функции, адаптированные к их потребностям, используя как схемы, так и языки описания оборудования на платформах разработки.Например, при разработке автоответчика, схемы и описания оборудования подготовлены и скомпилированы на компьютере.Используя кабель для загрузки, код передается в CPLD для программирования внутри системы, которое включает в себя тестирование, устранение неполадок и улучшение дизайнов.Успешно изготовленные конструкции затем производится массовым производством путем воспроизведения чипов CPLD.В таких проектах, как системы светофора, повторение процесса проектирования становится необходимым, аналогично восстановлению дома для восстановления своего новизны.Эта повторяющаяся методология часто закладывает основу для освоения, повышая как навыки, так и уверенность.

Ведущие варианты

На протяжении многих лет такие компании, как Altera, Lattice и Xilinx, обнародовали выдающиеся линии CPLD.Примечательные примеры включают Altera's EPM7128S, Решетчатые LC4128Vи Xilinx's XC95108 ПолемЭти модели нашли заметные роли в разных глобальных приложениях.Те, кто имел честь работать с этими различными продуктами, часто отмечают тонкие, но мощные различия, которые оптимизируют определенные функции.Это отражает процесс прекрасного отбора, на который влияют конкретные требования проекта, где каждый вариант имеет свою уникальную привлекательность.

Идентификация и классификация FPGA и CPLD

|

Аспект |

Cpld |

FPGA |

|

Формирование логического поведения |

Форма логического поведения с использованием структуры терминов продукта.

Примеры: серия решетки isplsi, серия Xilinx XC9500, Altera Max7000s

серия, серия решетки Маха |

Форма логического поведения с использованием метода поиска таблицы.

Примеры: Xilinx Spartan Series, Altera Flex10K, серия ACEX1K |

|

Пригодность |

Подходит для алгоритмов и комбинационной логики, работы

Лучше с ограниченными триггерами и богатыми терминами продукта |

Подходит для последовательной логики, лучше работает с

структуры, богатые триггерами |

|

Задержка срока |

Непрерывная структура проводки обеспечивает равномерную и

Предсказуемые временные задержки |

Сегментированная структура проводки приводит к непредсказуемому времени

задержки |

|

Гибкость программирования |

Фиксированные внутренние схемы изменяются для программирования.

Используется программирование на уровне логического блока |

Внутренняя проводка модифицирована для программирования.Логика

Программирование уровня затвора обеспечивает большую гибкость |

|

Интеграция |

Более низкая интеграция по сравнению с FPGA |

Более высокая интеграция с более сложной структурой проводки и

Логическая реализация |

|

Простота использования |

Проще в использовании с программированием с помощью E2PROM или FastFlash.

Внешний чип памяти не требуется |

Требуется внешняя память для хранения программирования

Информация, что приводит к более сложному использованию |

|

Скорость и предсказуемость |

Более высокая скорость и лучшая предсказуемость времени из -за

Смешанная взаимосвязь между логическими блоками |

Более медленная скорость и менее предсказуемое время из -за

Программирование на уровне затвора и распределенное взаимосвязь |

|

Технология программирования |

Использует программирование E2PROM или флэш -памяти.Данные программирования

сохраняется, когда система отключена.Поддерживает программирование на

программист или внутри система |

На основе программирования SRAM.Данные программирования теряются, когда

Система отключена и должна быть перезагружена.Поддерживает динамическую

конфигурация |

|

Конфиденциальность |

Предлагает лучшую конфиденциальность |

Обеспечивает более низкую конфиденциальность |

|

Энергопотребление |

Как правило, более высокое потребление мощности, особенно с

более высокая интеграция |

Более низкое энергопотребление по сравнению с CPLD |

Языки программирования CPLD

Анализ, как запрограммированы сложные программируемые логические устройства (CPLDS), является краеугольным камнем в создании универсальных аппаратных решений.Исторические методы программирования CPLD полагались на диаграммы лестницы или языки оборудования (HDL), причем Verilog HDL и VHDL являются преобладающим выбором.Выбранный язык может формировать как стратегию проектирования, так и оперативную эффективность реализаций.

• Verilog HDL: Verilog HDL берется за его простой синтаксис и надежные возможности моделирования, отражая методологии, используемые в проектировании цифровой логики.Его интеграция с инструментами электронных проектов автоматизации (EDA) позволяет беспрепятственно проводить синтез и моделирование.Наблюдается, что C-подобный синтаксис Verilog снижает барьер для входа для тех, у кого есть программирование, ускоряя путешествие от дизайна к развертыванию в широком спектре промышленных секторов.

• VHDL: VHDL предоставляет более сложный и выразительный вариант для программирования HDL.Часто это выбор для проектов, которые требуют дотошной документации и строгих признаков типов, признаков, оцененных в аэрокосмической и оборонной промышленности.Вы можете отметить, что, несмотря на потенциальную сложность VHDL в небольших проектах, его дисциплинированная структура поддерживает создание исключительно надежных дизайнов, необходимость в среде, где безопасность является доминирующей.

О нас

ALLELCO LIMITED

Прочитайте больше

Быстрое запрос

Пожалуйста, отправьте запрос, мы ответим немедленно.

NMOS Transistors: проектирование, эксплуатация и приложения

на 2024/12/29

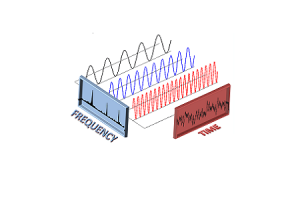

Быстрое преобразование Фурье (FFT): революция цифровой обработки сигналов

на 2024/12/29

Популярные посты

-

Комплексный набор инструкций: как они изменили вычисления?

на 8000/04/18 147760

-

Поспинка и функции USB-C

на 2000/04/18 111961

-

Использование примитивах Unified моделирования Xilinx: комплексное руководство по проектированию и моделированию FPGA

на 1600/04/18 111351

-

Напряжения источника питания в электронике: значение VCC, VDD, VEE, VSS и GND

на 0400/04/18 83729

-

Руководство по разъему RJ45: расписка, проводка, типы кабелей и использование

на 1970/01/1 79513

-

Конечное руководство по цветовым кодам проволоки в современных электрических системах

То, как наши электрические системы используют цвета, не только для внешнего вида.Каждый цвет провода теперь указывает на определенную функцию, что облегчает правильную идентификацию и обработку эле...на 1970/01/1 66930

-

Руководство по очистке клапана: функция, симптомы, тестирование и замена для оптимальной производительности двигателя

Клапан чистки является ключевой частью системы автомобиля, которая помогает поддерживать воздух в чистоте, управляя топливными парами, прежде чем они смогут сбежать в атмосферу.Это не только помога...на 1970/01/1 63078

-

Качество (Q) Фактор: уравнения и приложения

Коэффициент качества, или «Q», важен при проверке того, насколько хорошо индукторы и резонаторы работают в электронных системах, которые используют радиочастотные (RF).«Q» измеряет, насколько хорош...на 1970/01/1 63019

-

Достижение пиковой производительности с максимальной теоремой передачи мощности

Теорема максимальной передачи мощности объясняет, как энергия из источника, такого как батарея или генератор, течет к подключенной нагрузке.Он показывает точное условие, где нагрузка получает наибо...на 1970/01/1 54088

-

Спецификации батареи A23 и совместимость

Аккумулятор A23 представляет собой небольшую батарею в форме цилиндров с высоким напряжением.Также называется 23a, 23ae или Mn21, он работает на 12 вольт и намного выше, чем батареи AA или...на 1970/01/1 52160