EPM7064STC100-7 CPLD: функции, приложения и гид-руководство по программированию в системе

EPM7064STC100-7-это мощный чип из серии Intel Max® 7000S, предназначенный для выполнения сложных задач в электронных устройствах.В этом руководстве обсуждается основные функции и использование EPM7064STC100-7, подчеркивая его способность легко перепрограммировать, его быструю работу и гибкий дизайн.Этот чип, который идеально подходит для многих различных технологий, от небольших гаджетов до крупных промышленных машин, является ключевым элементом для создания передовых цифровых цепей.Каталог

EPM7064STC100-7 Описание

А EPM7064STC100-7 является сложным программируемым логическим устройством (CPLD) из серии Intel Max® 7000S.Он имеет 64 макроселлы и 1250 ворот, которые помогают в создании сложных цифровых цепей.Этот чип работает с максимальной скоростью 166,7 МГц с задержкой сигнала 7,5 наносекунд (NS).Он имеет 68 штифтов ввода/вывода (ввода/вывода), которые работают с логикой 3,3 В и 5 В, что облегчает использование в разных цепях.Ключевой функцией является его программируемость в системе 5,0 В (ISP) через интерфейс JTAG (IEEE 1149.1).Это означает, что вы можете перепрограммировать его, не удаляя его из схемы, облегчая тестирование и обновления.Он поставляется в 100-контактной плоской плоской пакете (TQFP), который представляет собой компактный, поверхностный пакет.Этот CPLD используется в встроенных системах, цифровой обработке сигналов, устройствах связи и промышленной автоматизации.

Мы предоставляем высококачественные компоненты и индивидуальные услуги, поэтому лучше всего разместить свой массовый заказ для надежных решений CPLD.

EPM7064STC100-7 Особенности

• Логика высокой плотности: EPM7064STC100-7 предназначен 64 макросовыми и 1250 полезными воротами, что делает его очень подходящим для реализации сложных логических функций в цифровых целях.Эта архитектура высокой плотности позволяет создавать сложные логические конструкции при сохранении эффективности в программируемых логических операциях.Хорошо оптимизированная структура макроселл обеспечивает эффективное использование доступных ресурсов, поддерживая расширенные комбинационные и последовательные логические реализации.

• Быстрая производительность: Построенный для высокоскоростной обработки, EPM7064STC100-7 работает с максимальной внутренней частотой 166,7 МГц, что позволяет быстро выполнять логические функции.Задержка его распространения в 7,5 нс обеспечивает минимальную задержку.Эта возможность быстрого переключения повышает способность устройства эффективно обрабатывать высокоскоростную обработку данных, кондиционирование сигналов и управление, что делает его надежным выбором для требовательных цифровых систем.

• Универсальный ввод -вывод: EPM7064STC100-7 с 68 программируемыми входными/выводами предлагает исключительную гибкость для интеграции в различные конструкции схемы.Поддерживая логические уровни 3,3 В и 5 В, он обеспечивает бесшовную совместимость с различными напряжениями системы, устраняя необходимость дополнительных переключателей уровня напряжения.Эта адаптивность делает его хорошо подходящим для приложений в средах смешанных напряжений, обеспечивая широкую применимость между встроенными системами, промышленным управлением и сети связи.

• Программируемость внутри системы (ISP): Одним из преимуществ EPM7064STC100-7 является его программируемость 5,0 В (ISP), облегченная через IEEE STD.1149.1 jtag interface.Эта функция позволяет перепрограммировать и изменять логические функции без падения или физического удаления устройства, упрощения технического обслуживания, отладки и итерационной разработки.Возможность ISP уменьшает время простоя и повышает гибкость обновлений прошивки, что делает его бесценным для динамических и реконфигурируемых цифровых проектов.

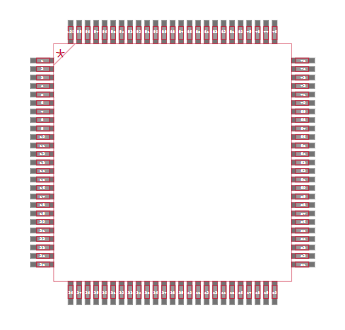

EPM7064STC100-7 Модели CAD

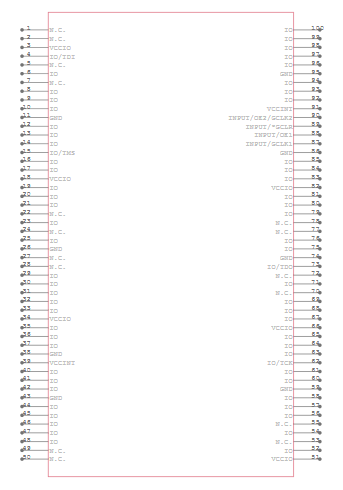

EPM7064STC100-7 Символ

EPM7064STC100-7 Footprint

EPM7064STC100-7 3D-модель

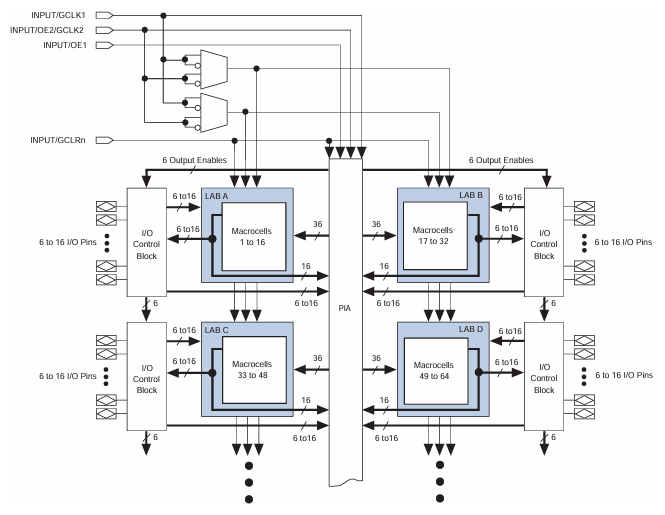

EPM7064STC100-7 Блок-схема

А EPM7064STC100-7 Блок-схема Показывает, как логические элементы чипа подключены и контролируются.Он содержит четыре логических массива (LAB), помеченные A, B, C и D, каждый содержит 16 макроселлов.Эти макроселлы выполняют логические функции, и они подключаются через программируемый межконтактный массив (PIA), который обеспечивает гибкую маршрутизацию сигналов.Каждая лаборатория связана с управляющим блоком ввода -вывода, обрабатывая до 16 входных/выводных контактов на лабораторию.Диаграмма также показывает глобальные контрольные сигналы (GCLK1, GCLK2, OE1 и GCLRN), которые помогают управлять функциями сброса и сброса для чипа.Некоторые логические ворота обрабатывают эти сигналы, прежде чем они достигнут разных частей системы.Конструкция EPM7064STC100-7 позволяет использовать его в различных программируемых логических приложениях, таких как государственные машины, декодирование адресов и другие пользовательские цифровые цепи.Его гибкие взаимосвязи обеспечивают эффективный поток сигнала и надежную работу.

EPM7064STC100-7 спецификации

|

Тип |

Параметр |

|

Производитель |

Altera/Intel |

|

Ряд |

Max® 7000S |

|

Упаковка |

Поднос |

|

Статус частично |

Устаревший |

|

Программируемый тип |

В системном программируемом |

|

Время задержки TPD (1) Макс |

7,5 нс |

|

Поставка напряжения - внутреннее |

4,75 В ~ 5,25 В. |

|

Количество логических элементов/блоков |

4 |

|

Количество макросел |

64 |

|

Количество ворот |

1250 |

|

Номер в/вывода |

68 |

|

Рабочая температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажный тип |

Поверхностное крепление |

|

Пакет / корпус |

100-TQFP |

|

Пакет устройства поставщика |

100-TQFP (14x14) |

|

Базовый номер продукта |

EPM7064 |

Последовательность программирования EPM7064STC100-7 в рамках программирования (ISP)

EPM7064STC100-7, часть семейства CPLD MAX 7000S, следует за шестиступенчатой последовательности программирования внутри системы (ISP), чтобы обеспечить правильную конфигурацию.Этот процесс позволяет запрограммировать устройство, не удаляя его с платы.Процесс ISP включает в себя изменение инструкций, адресов и данных через PIN -код TDI (тестовые данные в) при получении ответов через PIN -код TDO (тестовые данные).

Первый этап, Введите ISP, гарантирует, что контакты ввода/вывода плавно переходят от режима пользователя в режим интернет -провайдера и требуют приблизительно 1 мс.За этим следует Проверьте удостоверение личности, где кремниевый идентификатор устройства считывается, чтобы подтвердить правильную цель.Далее Объемная стирания Сдвиг стадии в инструкциях стирания и применяет импульс на 100 мс, очищая все существующие данные в клетках EEPROM.А Программа Следуют этапа, где адреса и данные последовательно перемещаются в устройство, применяя программирующие импульсы для настройки ячеек eEPROM.Каждый адрес должен быть запрограммирован индивидуально, делая этот шаг трудоемким, в зависимости от количества ячеек eEPROM в устройстве.

После завершения программирования Проверять Этап гарантирует, что данные хранятся правильно.Здесь импульсы считываются на ячейки EEPROM, и полученные данные сравниваются с ожидаемыми значениями.Если обнаружены расхождения, может потребоваться перепрограммирование.Наконец Выйдите из ISP Стадия гарантирует, что выводы ввода -вывода возвращаются в пользовательский режим, требуя еще 1 мс.На общее время программирования или проверки влияет два основных фактора: время импульса, необходимое для операций EEPROM, программирования и операций чтения, и время смещения, что зависит от частоты TCK (тестовые часы) и количества циклов, необходимых для передачи инструкций, адресов и данных.Поскольку различные устройства, способствующие ISP, имеют различное количество ячеек eEPROM, общее фиксированное и переменное время уникальны для каждого устройства.Общее время провайдера может быть рассчитано как функция частоты TCK, количества целевых устройств и архитектуры EEPROM.

EPM7064STC100-7 Приложения

Встроенные системы

EPM7064STC100-7 широко используется в приложениях встроенных систем, где он служит гибким программируемым логическим решением для управления различными периферийными устройствами, сигналами обработки и реализации пользовательских протоколов.Его способность взаимодействовать с микроконтроллерами и датчиками позволяет оптимизировать производительность системы, сохраняя при этом компактный след.Благодаря высокоскоростной работе и низким энергопотреблению, это отличный выбор для встроенных приложений, которые требуют надежности и эффективности.

Цифровая обработка сигнала (DSP)

При цифровой обработке сигналов EPM7064STC100-7 играет роль в реализации фильтров, модуляции сигналов и различных математических функций.Его быстрые скорости переключения и низкая задержка распространения делают его подходящим для выполнения высокочастотных задач обработки данных, обеспечивая минимальную задержку в преобразовании и манипуляции сигнала.Он обычно используется в обработке аудио, телекоммуникациях и радиолокационных системах.

Передача данных

EPM7064STC100-7 широко используется в сетевых системах и системах связи данных из-за его способности обрабатывать логические операции, такие как маршрутизация данных, буферизация и коррекция ошибок.Его программируемые возможности ввода/вывода позволяют ему адаптироваться к различным протоколам связи, что делает его ценным компонентом в коммутаторах Ethernet, маршрутизаторах и телекоммуникационной инфраструктуре.Его поддержка программируемости внутри системы (ISP) также позволяет обновлять поля, улучшая адаптивность в средах динамических сетевых технологий.

Промышленная автоматизация

Промышленные приложения требуют высокой надежности, долговечности и низкого энергопотребления, что делает EPM7064STC100-7 предпочтительным выбором для программируемых логических контроллеров (ПЛК), систем управления двигателями и автоматизированного тестирования.Благодаря своей в систему программируемости на основе JTAG он обеспечивает возможность совершенствовать процессы автоматизации, не требуя физического удаления или перепроектирования.Его универсальность в совместимости напряжения также делает его подходящим для взаимодействия с широким спектром датчиков и приводов, используемых в промышленных условиях.

EPM7064STC100-7 Аналогичные детали

EPM7064STC100-7 Преимущества

Программируемость внутри системы (ISP)

Одним из самых больших преимуществ EPM7064STC100-7 является его способность перепрограммировать, пока все еще установлена в системе.Это устраняет необходимость удаления чипа для обновлений, сокращения времени обслуживания и повышения эффективности.Вы можете реализовать модификации дизайна без прерывания производства, что делает его экономически эффективным решением для долгосрочных проектов.

Высокоскоростная производительность

Устройство поддерживает высокую внутреннюю частоту работы до 166,7 МГц, что позволяет быстро обрабатывать данные и время обработки данных.Это делает его идеальным для приложений, требующих обработки сигналов, логического управления и высокоскоростного взаимодействия, обеспечивая более плавную и надежную работу системы.

Универсальная поддержка ввода/вывода

С до 68 настраиваемыми контактами ввода/вывода и совместимостью с несколькими уровнями напряжения (3,3 В, 5 В и толерантными параметрами для 2,5 В, 3,3 В и 5 В), EPM7064STC100-7 предлагает гибкость в конструкции системы.Это обеспечивает бесшовную интеграцию в различные схемы и поддерживает смешанные среды, уменьшая проблемы совместимости с другими компонентами.

Надежная работа в разных средах

EPM7064STC100-7, разработанный для функционирования в диапазоне температур от 0 ° C до 70 ° C, обеспечивает последовательную и стабильную работу в различных условиях.Эта надежность делает его предпочтительным выбором для приложений, где требуется стабильность окружающей среды, такие как промышленная автоматизация, телекоммуникации и встроенные системы управления.

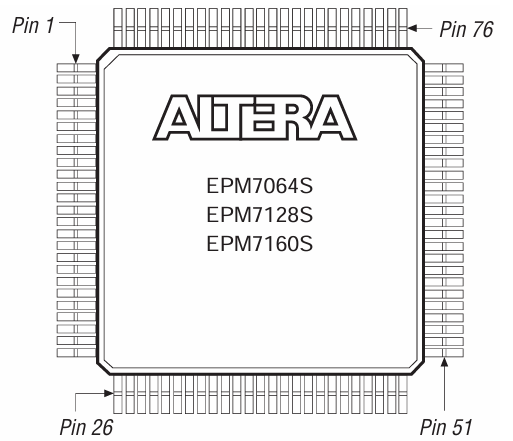

EPM7064STC100-7 Пакет Диаграмма пин-аута

EPM7064STC100-7 представляет собой CPLD (сложное программируемое логическое устройство) из серии Altera Max 7000S, размещенная в 100-контактной Flat Plat Package (TQFP-100).Этот тип пакета предназначен для применений поверхностного монтажа, предлагая баланс высокой плотности штифта и компактного размера.А Диаграмма пин-аута Следует за схемой нумерации против часовой стрелки с PIN 1, расположенным в верхнем левом углу пакета.Перемещение против часовой стрелки первые 25 контактов занимают левую сторону, контакты от 26 до 50 расположены вдоль нижнего края, контакты от 51 до 75 продолжаются вдоль правой стороны, а контакты от 76 до 100 распределены вдоль верхнего края.А TQFP-100 Пакет Особенности тонкие отведения, простирающиеся наружу от всех четырех сторон плоского квадратного тела.Эта конструкция повышает совместимость с поверхностным собранием, сохраняя при этом адекватное расстояние между штифтами для легкой пайки и сборки.Выводящий шаг (расстояние между соседними булавками), как правило, составляет 0,5 мм, оптимизируя целостность сигнала, в то же время минимизируя общую площадь.

EPM7064STC100-7 Производитель

EPM7064STC100-7-это CPLD (сложное программируемое логическое устройство), первоначально разработанное Altera, полупроводниковой компанией, известной своими программируемыми логическими решениями.В 2015 году, Intel Получил Altera, интегрируя свои линейки продуктов FPGA и CPLD в группу программируемых решений Intel (PSG).С тех пор EPM7064STC100-7 был маркирован в соответствии с Intel, хотя он был помечен как устаревший.Intel, как производитель, сохранил Legacy Support для CPLD серии Max® 7000S, включая эту модель, постепенно смещая свое внимание на современные FPGA и программируемые логические технологии.

Заключение

EPM7064STC100-7 объединяет сложные функции, быстрые производительности и простые обновления в одном чипе, доказывая ее ценность в сложных цифровых настройках.Это руководство показало, как он работает, для чего оно используется и как оно вписывается в различные электронные системы.Это помогает, чтобы устройства работали гладко и эффективно, доказывая, что это все еще очень полезно для многих приложений.Это руководство дает четкое представление о том, как EPM7064STC100-7 может помочь улучшить электронные конструкции и системы системы.

DataSheet PDF

EPM7064STC100-7 DataShets:

О нас

ALLELCO LIMITED

Прочитайте больше

Быстрое запрос

Пожалуйста, отправьте запрос, мы ответим немедленно.

Часто задаваемые вопросы [FAQ]

1. Как задержка распространения 7,5NS размножения EPM7064STC100-7

Задержка распространения 7,5NS обеспечивает обработку сигналов с низкой задержкой, что делает этот CPLD подходящим для высокоскоростных приложений, таких как цифровые сигналы (DSP), системы связи и промышленная автоматизация, которая требует точного управления временем.

2. Можно ли запрограммировать EPM7064STC100-7 с использованием современных инструментов разработки?

Да, его можно запрограммировать с использованием программного обеспечения Intel Quartus II (ранее Altera Quartus) вместе с соответствующим программистом JTAG.Тем не менее, поддержка более старых CPLD, таких как EPM7064STC100-7, может быть ограничена в более новых версиях квартала, поэтому вам может потребоваться использовать устаревшие версии, такие как Quartus II 13.0 SP1, который по-прежнему поддерживает устройства серии Max® 7000S.

3. Поддерживает ли EPM7064STC100-7.

Да, он поддерживает логические уровни 3,3 В и 5 В, что делает его совместимым с широким спектром цифровых цепей.Эта гибкость полезна для взаимодействия компонентов Legacy 5V с современными системами 3,3 В без дополнительных схем изменения уровня.

4. Какой лучший метод для устранения неполадок в EPM7064STC100-7 Design?

Для устранения неполадок вы можете использовать логический анализатор Quartus SignalTAP II или внешние осциллографы и логические анализаторы для мониторинга сигналов.При отладке вопросов программирования JTAG убедитесь, что соединения TDI, TDO, TCK и TMS являются правильными и что вы используете совместимый программист USB Blaster или Byteblastermv.

5. Могу ли я запрограммировать EPM7064STC100-7, не удаляя его с моей платы?

Да.Программируемость внутри системы 5,0 В (ISP) через JTAG (IEEE 1149.1) позволяет перепрограммировать устройство, пока оно остается в системе.Это делает обновления прошивки, отладку и тестирование гораздо более эффективными по сравнению с традиционными CPLD.

Полное руководство по резистору 10K: цветовой код, приложения и схема использования

на 2025/03/10

Конденсаторы против батарей: что лучше всего подходит для ваших потребностей в энергетике?

на 2025/03/7

Популярные посты

-

Комплексный набор инструкций: как они изменили вычисления?

на 8000/04/18 147760

-

Поспинка и функции USB-C

на 2000/04/18 111969

-

Использование примитивах Unified моделирования Xilinx: комплексное руководство по проектированию и моделированию FPGA

на 1600/04/18 111351

-

Напряжения источника питания в электронике: значение VCC, VDD, VEE, VSS и GND

на 0400/04/18 83732

-

Руководство по разъему RJ45: расписка, проводка, типы кабелей и использование

на 1970/01/1 79520

-

Конечное руководство по цветовым кодам проволоки в современных электрических системах

То, как наши электрические системы используют цвета, не только для внешнего вида.Каждый цвет провода теперь указывает на определенную функцию, что облегчает правильную идентификацию и обработку эле...на 1970/01/1 66930

-

Руководство по очистке клапана: функция, симптомы, тестирование и замена для оптимальной производительности двигателя

Клапан чистки является ключевой частью системы автомобиля, которая помогает поддерживать воздух в чистоте, управляя топливными парами, прежде чем они смогут сбежать в атмосферу.Это не только помога...на 1970/01/1 63080

-

Качество (Q) Фактор: уравнения и приложения

Коэффициент качества, или «Q», важен при проверке того, насколько хорошо индукторы и резонаторы работают в электронных системах, которые используют радиочастотные (RF).«Q» измеряет, насколько хорош...на 1970/01/1 63024

-

Достижение пиковой производительности с максимальной теоремой передачи мощности

Теорема максимальной передачи мощности объясняет, как энергия из источника, такого как батарея или генератор, течет к подключенной нагрузке.Он показывает точное условие, где нагрузка получает наибо...на 1970/01/1 54090

-

Спецификации батареи A23 и совместимость

Аккумулятор A23 представляет собой небольшую батарею в форме цилиндров с высоким напряжением.Также называется 23a, 23ae или Mn21, он работает на 12 вольт и намного выше, чем батареи AA или...на 1970/01/1 52163