EPM7192SQC160-15 CPLD: функции, разгона, программирование и приложения

В этом руководстве рассказывается о EPM7192SQC160-15, программируемом логическом чипе из семейства MAX 7000S.Это объясняет, что может сделать чип, как он работает и где его можно использовать.Он показывает, как чип встроен внутри, что делает каждый вывод и как он подключается к другим деталям.Руководство также включает в себя, где можно использовать этот чип, как программировать его шаг за шагом, какие другие подобные чипы существуют и кто делает его.Каталог

Что такое EPM7192SQC160-15?

А EPM7192SQC160-15 является средним уровнем CPLD (комплексное программируемое логическое устройство) из семейства Max 7000S, созданного для надежного управления цифровым логикой во встроенных и промышленных системах.Этот чип предлагает 192 макроселлы и около 3750 логических ворот, обеспечивая достаточную мощность для выполнения умеренных логических задач.Он включает в себя 124 вывода ввода/вывода и работает на подаче 5 В, с многоэтажной поддержкой ввода -вывода для взаимодействия с логическими системами 3,3 В и 5 В.Его встроенная программируемая архитектура на основе EEPROM означает, что вы можете перепрограммировать ее непосредственно в вашей схеме, используя JTAG, без необходимости дополнительных компонентов или внешней памяти.Благодаря скорости –15 он поддерживает системные тактовые частоты до 76,9 МГц, предлагая быстрой и последовательной производительности времени для широких цифровых приложений.Семейство Max 7000S известна своей твердой производительностью, памятью EEPROM и гибкой операцией напряжения.

Ищете EPM7192SQC160-15?Свяжитесь с нами, чтобы проверить текущие запасы, время выполнения заказа и цены.

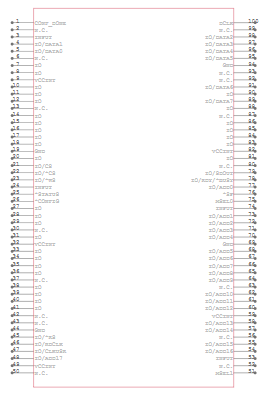

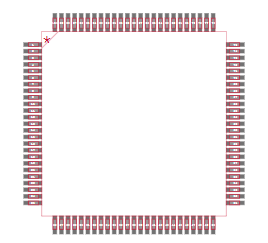

EPM7192SQC160-15 CAD модели

EPM7192SQC160-15 Символ

EPM7192SQC160-15

EPM7192SQC160-15 3D модель

EPM7192SQC160-15 Особенности

192 макроселлы: Устройство включает в себя 192 макроселлы, которые служат основными программируемыми элементами.Эти макросовые машины могут быть настроены для реализации широкого спектра комбинационных и последовательных логических функций, необходимых для цифровых проектов.

Приблизительно 3750 логических ворот: Он предлагает эквивалентную логическую емкость около 3750 ворот, что делает ее подходящей для логики управления средней комплексностью, государственных машин или логики клей во встроенных системах.

Программируемость внутри системы через JTAG: Он имеет память на основе EEPROM, которая позволяет перепрограммировать непосредственно в системе, используя стандартный интерфейс JTAG, поддерживая как стандарты IEEE 1149.1 и IEEE 1532.

Максимальная частота до 125 МГц: Внутренняя логика может работать на тактовых скоростях, достигающих 125 МГц, что позволяет быстрая обработка для чувствительных к времени приложений.

Задержка распространения 7,5 нс: Чип предлагает низкую задержку распространения приблизительно 7,5 наносекунд, обеспечивая быстрый отклик сигнала от ввода на выход.

Поддерживает предложение 5 В с помощью многоэтажного ввода -вывода: Устройство работает на подаче ядра 5V и поддерживает многоэтажный ввод-вывод, позволяющий совместимости с уровнями сигналов 5 В и 3,3 В для легкой интеграции в системы смешанного напряжения.

Программируемая скорость нажатия и выходы с открытым дреном: Вы можете управлять скоростями краев сигнала для уменьшения EMI и выбрать выходы с открытым дризоном для сдвига с проводной и логикой или уровнем.

Шесть глобальных результатов включает сигналы: Эти глобальные контрольные сигналы позволяют включать или отключить выходы в нескольких банках ввода -вывода для эффективного управления сигналами.

Настраиваемые шлепанцы в макроселлах: Каждая макроселла включает в себя триггер, который поддерживает предустановленную, прозрачную, так и индивидуально управлять, обеспечивая повышенную гибкость для последовательной логической конструкции.

Режим низкой мощности: Устройство включает в себя функцию энергосбережения, которая может сократить потребление мощности макроселля более чем на 50%, что полезно для энергоэффективных применений.

Поддержка тестового сканирования JTAG : Устройства с 128 или более макросолями, такие как этот, включают в себя полные функции тестирования границы для эффективной диагностики и валидации на уровне доски.

Бит безопасности для защиты дизайна: Программируемый бит безопасности гарантирует, что внутренний дизайн не может быть прочитал или скопирован, защищая интеллектуальную собственность.

ПКИ-совместимый вводный/вывод: Структура ввода/вывода предназначена для удовлетворения требований к электрическому PCI, что обеспечивает прямое взаимодействие с системами на основе PCI.

Диапазон рабочей температуры от 0 ° C до 70 ° C: Стандартный диапазон температуры коммерческого класса делает это устройство подходящим для большинства приложений в помещении и контролируемой среде.

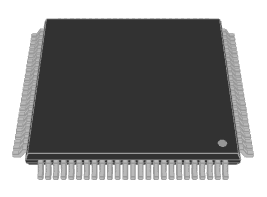

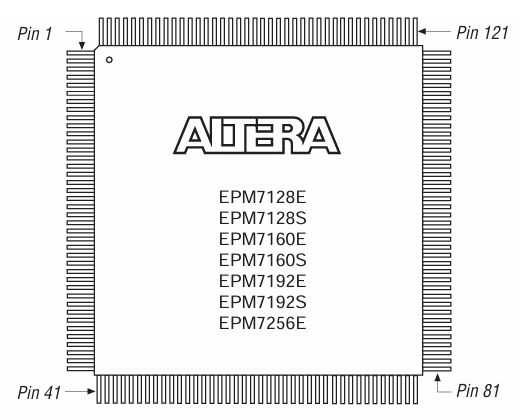

EPM7192SQC160-15 Диаграмма пинок

Эта диаграмма показывает компоновку PIN для EPM7192SQC160-15 и аналогичных устройств Altera Max 7000S.Чип имеет 160 контактов, расположенных вокруг всех четырех сторон в квадратном пакете QFP.PIN 1 начинается в верхнем левом углу, а цифры идут против часовой стрелки вокруг чипа.Каждая сторона имеет 40 булавок.Маленькая точка на верхнем левом штифте 1, которая помогает при правильном размещении.Название чипа в центре показывает, что он совместим с другими моделями в той же семье.Этот макет обеспечивает много подключений ввода/вывода и полезна для сложных логических конструкций.

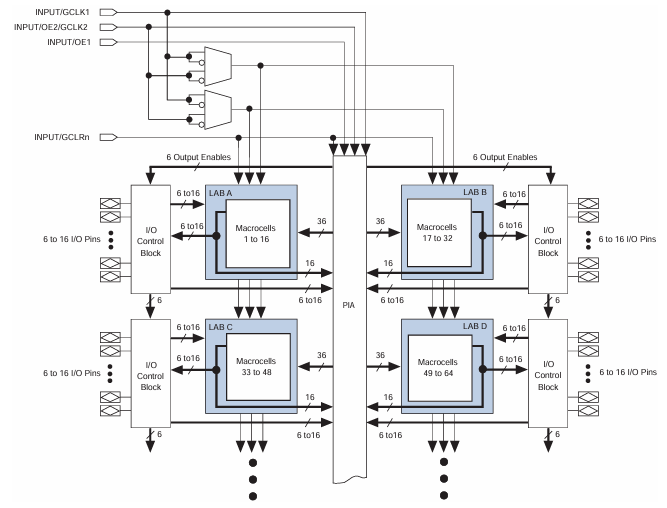

Блок -схема максимума 7000S

Эта блочная диаграмма показывает внутреннюю структуру CPLD MAX 7000S, включая EPM7192SQC160-15.Чип делится на четыре основных секция, называемые логическими массивными блоками (лаборатория A до D).Каждая лаборатория имеет 16 макроэнкл, которые представляют собой небольшие логические единицы, используемые для построения цифровых цепей.Вместе эти лаборатории обрабатывают сложные логические операции.

В центре находится программируемый массив Interconnect (PIA), который соединяет все лаборатории и позволяет им обмениваться данными.Каждая лаборатория отправляет и получает сигналы через 36 каналов, обеспечивая гибкую маршрутизацию между логическими блоками.По краям есть блоки управления вводами/выводом, которые связывают 6 с 16 контактами ввода -вывода с каждой лабораторией, что позволяет устройству подключаться с другими частями системы.

Вверху отображаются глобальные сигналы управления, такие как часы и вывод.Эти сигналы помогают управлять тем, как данные перемещаются внутри чипа и когда выходы активны.В целом, диаграмма показывает, как EPM7192SQC160-15 организует свою логику и соединения для поддержки пользовательских цифровых проектов.

EPM7192SQC160-15 Спецификации

|

Тип |

Параметр |

|

Производитель |

Альтерна |

|

Ряд |

Max® 7000S |

|

Упаковка |

Поднос |

|

Статус частично |

Устаревший |

|

Программируемый тип |

В системном программируемом |

|

Время задержки TPD (1) Макс |

15 нс |

|

Поставка напряжения - внутреннее |

4,75 В ~ 5,25 В. |

|

Количество логических элементов/блоков |

12 |

|

Количество макросел |

192 |

|

Количество ворот |

3750 |

|

Номер в/вывода |

124 |

|

Рабочая температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажный тип |

Поверхностное крепление |

|

Пакет / корпус |

160-BQFP |

|

Пакет устройства поставщика |

160-pqfp (28x28) |

|

Базовый номер продукта |

EPM7192 |

EPM7192SQC160-15 Приложения

Встроенная система клей для системы

EPM7192SQC160-15 идеально подходит для преодоления различных цифровых устройств во встроенных системах.Его можно использовать для управления связи между микроконтроллерами, чипами памяти и устройствами ввода -вывода путем обработки декодирования адреса, управления шиной и регулировки времени без необходимости дискретных логических ICS.

Государственные машины и логика управления

Благодаря 192 макроселлам чип хорошо подходит для реализации пользовательских машин и логики управления.Он обычно используется в задачах автоматизации, контроллерах двигателей и системах управления на основе времени, которые требуют надежных и повторяющихся переходов состояния.

Интерфейсы протокола связи

Этот CPLD может быть запрограммирован на создание или перевод протоколов связи, таких как UART, SPI, I²C или пользовательские серийные форматы.Это обеспечивает легкую конфигурацию и модификацию без изменения аппаратного обеспечения, что делает его ценным для взаимодействия связи.

Предварительная обработка цифрового сигнала

Благодаря своей быстрой логической скорости и низкой задержке распространения, он может обрабатывать простые задачи обработки сигналов, такие как фильтрация, мультиплексирование или обнаружение краев, прежде чем сигналы достигают основного процессора или чипа DSP.

Перевод интерфейса и смещение уровня

Его многоэтажная способность ввода/вывода поддерживает как 3,3 В, так и 5V сигналов.Это делает его подходящим для конструкций, которые включают компоненты, работающие на разных уровнях напряжения, что позволяет безопасному и эффективному переводу напряжения.

Быстрое прототипирование и обновления внутри системы

Вы можете использовать этот чип в системах, которые могут потребовать частых логических обновлений.Его структура на основе EEPROM и интерфейс программирования JTAG позволяют перепрограммировать логику даже после сборки платы.

Тест на уровне доски и диагностика

При поддержке границы через JTAG он проверяет соединения между чипами на печатной плате без необходимости датчиков.Это полезно во время производства и диагностики в поле для обнаружения проблем пайки или маршрутизации.

EPM7192SQC160-15 Аналогичные части

• EPM7192EQC160-20 (Altera)

Это устройство из той же серии Max 7000 и предлагает те же логические ресурсы, 192 Macrocells и 124 вывода ввода/вывода в 160-контактном пакете PQFP.Он работает с более медленной скоростью –20, что означает, что он имеет более длительные задержки распространения (~ 20 нс), но все же отвечает потребностям не критических конструкций.Это подходящая альтернатива для приложений, где важна логическая плотность, но ультрастрабильное время не является приоритетом, что делает ее идеальным для чувствительных к затратам проектов, которые по-прежнему нуждаются в функциональной эквивалентности.

• EPM7192SQI160-10N (Altera)

Эта часть также совместима с логикой с EPM7192SQC160-15, предлагая такое же количество макроселлов и I/OS.Тем не менее, он использует –10 -скоростную оценку, которая поддерживает более быструю работу с улучшением времени (задержка распространения 10 нс).Он также поддерживает расширенный диапазон температуры от –40 ° C до +85 ° C, что делает его отличной заменой промышленного или наружного применения.Это делает его идеальным, когда требуется более высокая скорость и экологическая устойчивость.

• EPM7192SQC160-7 (Intel)

В качестве прямого ускорения варианта EPM7192SQC160-15 версия -7 обеспечивает самую быструю производительность в семье, а распространение задерживается до 7,5 нс.Он поддерживает ту же конфигурацию PIN-кода, характеристики питания и логическую плотность, предлагая замену замены для тех, кто ищет лучшую скорость без изменения макета платы или требований к напряжению.Это делает его лучшим выбором для критических проектов, нуждающихся в более быстром отклике сигнала, оставаясь в пределах одного и того же дизайна.

EPM7192SQC160-15 Шаги программирования

1. Введите режим ISP

Первый шаг-перевести устройство в режим ISP (внутри системы программирования).Это делается через интерфейс JTAG.Оказавшись в режиме интернет-провайдера, все штифты ввода/вывода на устройстве помещаются в безопасное режим три-состояния, чтобы предотвратить непреднамеренные логические помехи во время программирования.Эта инициализация обычно занимает около 1 миллисекунды.

2. Проверьте идентификатор устройства

Уникальный кремниевый идентификатор встроен в устройство, чтобы убедиться, что это правильная модель до начала программирования.Система смещается в инструкции чтения и извлекает идентификатор через строку TDO (тестовые данные).Эта проверка гарантирует, что инструмент программирования подключен к правой CPLD и избегает таких ошибок, как перезапись другой части.

3. Основная стирания

Основная стирания очищает все ранее хранящиеся данные в памяти EEPROM CPLD.Это готовит чип для получения новой конфигурации.Команда стирания инициирует импульс, который обычно длится около 100 миллисекунд, обеспечивая сброс всех программируемых клеток.

4. Программа eeprom

Новые данные конфигурации загружаются в устройство путем перемещения адреса и битов данных через порт JTAG.Каждая ячейка памяти записана один за другим, с импульсом программирования, применяемым после каждого успешного цикла записи.Этот процесс определяет логическую структуру, которую CPLD будет использовать при питании.

5. Проверьте EEPROM

После программирования устройство выполняет шаг проверки.Это включает в себя чтение каждого запрограммированного местоположения памяти и сравнение выходных значений с предполагаемыми данными.Если проверка не удается, процесс должен быть повторен.Этот шаг гарантирует, что конфигурация была успешно написана.

6. Выйдите из режима ISP

После завершения проверки выпускается окончательная команда для выхода из режима ISP.Устройство реактивирует свои контакты ввода/вывода и возобновляет нормальную работу.Этот переход также занимает около 1 миллисекунды и завершает цикл программирования внутри системы.

EPM7192SQC160-15 Размеры упаковки

• Размер тела: 28 мм × 28 мм

• Высота упаковки: 3,4 мм

• Штифт: 0,65 мм

EPM7192SQC160-15 Производитель

EPM7192SQC160-15 был первоначально изготовлен Altera Corporation, компания, известная своими усовершенствованными программируемыми логическими устройствами.В 2015 году Altera была приобретена Intel Corporationи в настоящее время устройство является частью группы программируемых решений Intel в семье Max 7000S CPLD.Intel продолжает поддерживать Legacy Altera Products, хотя EPM7192SQC160-15 в настоящее время классифицируется как устаревшая в большинстве официальных каталогов.Несмотря на прекращенный статус, историческая репутация Intel за надежность и наследие Altera в высокопроизводительных логических решениях обеспечивает дальнейший спрос и доступность через вторичные дистрибьюторы.

Заключение

EPM7192SQC160-15 является полезным и гибким чипом для обработки задач цифрового управления во многих электронных системах.Он предлагает достаточно логической мощности для таких работ, как создание пользовательских государственных машин, обработка сигналов и подключение различных устройств.Он поддерживает различные уровни напряжения, работает на быстрых скоростях и может легко обновляться с помощью JTAG.Его внутренняя конструкция обеспечивает плавный поток сигнала и легкие изменения логики.Несмотря на то, что теперь это прекращено, это все еще является отличным вариантом для старых или текущих проектов, и его можно заменить аналогичными чипами, которые предлагают более быструю или более широкую поддержку температуры.

DataSheet PDF

EPM7192SQC160-15 Datahasthes:

О нас

ALLELCO LIMITED

Прочитайте больше

Быстрое запрос

Пожалуйста, отправьте запрос, мы ответим немедленно.

Часто задаваемые вопросы [FAQ]

1. Могу ли я запрограммировать EPM7192SQC160-15, не удаляя его с платы?

Да, чип поддерживает программирование внутри системы (ISP) через интерфейс JTAG, поэтому вы можете программировать или перепрограммировать его напрямую, пока он припаянный на печатной плате, что упрощает обновления проектирования и уменьшает переделку.

2. Какое программное обеспечение для программирования я должен использовать для EPM7192SQC160-15?

Вы можете использовать программное обеспечение Altera Quartus II (более старые версии) для создания логических проектов, составления кода и управления процессом программирования на основе JTAG.Quartus II поддерживает устройства Max 7000S, такие как EPM7192SQC160-15.

3. требует ли EPM7192SQC160-15 внешней памяти для работы?

Нет, он имеет внутреннюю конфигурационную память на основе EEPROM.Вся логическая конфигурация хранится внутри чипа, поэтому для хранения логических состояний или последовательностей загрузки не требуется внешняя память.

4. Что делает EPM7192SQC160-15 подходящим для промышленного использования?

Его надежная работа 5V, совместимость ввода/вывода, быстрой логической обработки и нелетуальная память, основанная на EEPROM, делают ее надежной для промышленных систем, которые требуют стабильных и долговечных функций цифровой логики.

5. Как EPM7192SQC160-15 Смешанные системы напряжения?

Благодаря своей поддержке ввода-вывода в/выводе, устройство может взаимодействовать с логическими уровнями 3,3 В и 5 В, что делает его идеальным для систем смешанного сигнала и взаимодействует с современными низковольтными компонентами.

Почему выбирают EPF10K100EFC484-3 для вашего проекта

на 2025/06/13

Что такое переключатель SPST и как он работает?

на 2025/06/12

Популярные посты

-

Комплексный набор инструкций: как они изменили вычисления?

на 8000/04/18 147758

-

Поспинка и функции USB-C

на 2000/04/18 111958

-

Использование примитивах Unified моделирования Xilinx: комплексное руководство по проектированию и моделированию FPGA

на 1600/04/18 111349

-

Напряжения источника питания в электронике: значение VCC, VDD, VEE, VSS и GND

на 0400/04/18 83726

-

Руководство по разъему RJ45: расписка, проводка, типы кабелей и использование

на 1970/01/1 79510

-

Конечное руководство по цветовым кодам проволоки в современных электрических системах

То, как наши электрические системы используют цвета, не только для внешнего вида.Каждый цвет провода теперь указывает на определенную функцию, что облегчает правильную идентификацию и обработку эле...на 1970/01/1 66929

-

Руководство по очистке клапана: функция, симптомы, тестирование и замена для оптимальной производительности двигателя

Клапан чистки является ключевой частью системы автомобиля, которая помогает поддерживать воздух в чистоте, управляя топливными парами, прежде чем они смогут сбежать в атмосферу.Это не только помога...на 1970/01/1 63078

-

Качество (Q) Фактор: уравнения и приложения

Коэффициент качества, или «Q», важен при проверке того, насколько хорошо индукторы и резонаторы работают в электронных системах, которые используют радиочастотные (RF).«Q» измеряет, насколько хорош...на 1970/01/1 63017

-

Достижение пиковой производительности с максимальной теоремой передачи мощности

Теорема максимальной передачи мощности объясняет, как энергия из источника, такого как батарея или генератор, течет к подключенной нагрузке.Он показывает точное условие, где нагрузка получает наибо...на 1970/01/1 54086

-

Спецификации батареи A23 и совместимость

Аккумулятор A23 представляет собой небольшую батарею в форме цилиндров с высоким напряжением.Также называется 23a, 23ae или Mn21, он работает на 12 вольт и намного выше, чем батареи AA или...на 1970/01/1 52153