XC2S50-5TQG144I FPGA: функции, спецификации, приложения и руководство по программированию

XC2S50-5TQG144I-это гибкий и мощный FPGA (полевой программируемый массив ворот) из семейства Spartan-II Amd Xilinx.Он предназначен для цифровых проектов, которые нуждаются в настройке, скорости и надежности.Это руководство объясняет функции, спецификации, процесс программирования и использование этой FPGA, чтобы помочь вам понять, как максимально использовать его.Каталог

XC2S50-5TQG144I Обзор

А XC2S50-5TQG144I это Spartan-II FPGA от AMD Xilinx, разработанная для цифровых проектов, которые нуждаются в гибкости и производительности.Он имеет 50 000 системных ворот и 1728 логических ячеек, позволяющих выполнять сложные задачи.Чип включает в себя 384 настраиваемые логические блоки (CLBS) и 32 768 битов ОЗУ, что дает ему хорошую память и мощность обработки.С 92 выводами ввода/вывода (ввода/вывода) он может легко подключаться к другим компонентам.Он поставляется в 144-контактной тонкой квадочной плоской пакете (TQFP), который является компактным и простым в использовании.FPGA работает на 2,5 В (с безопасным диапазоном от 2,375 В до 2,625 В) и хорошо работает при температуре от -40 ° C до +100 ° C.Эта Spartan-II FPGA производится с помощью 0,18-микронной технологии, что делает ее эффективной и надежной.Он программируется, то есть вы можете обновить его функции по мере необходимости.

Для экономически эффективного, высокоэффективного решения, размещение с нами объемное заказ является оптимальным выбором, обеспечивая превосходное качество.

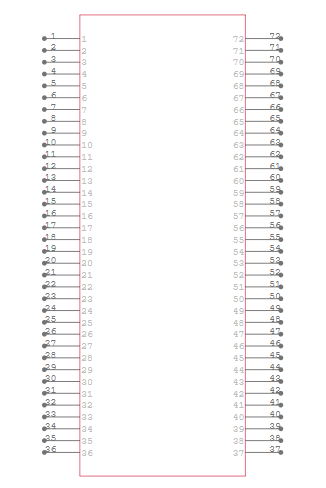

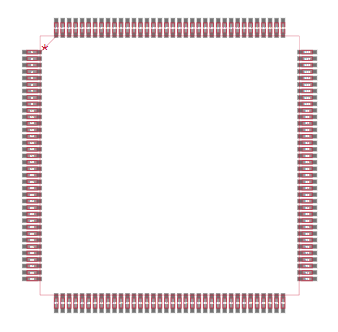

XC2S50-5TQG144I CAD модели

XC2S50-5TQG144I Символ

XC2S50-5TQG144I

XC2S50-5TQG144I 3D модель

XC2S50-5TQG144I Особенности

• Системные ворота: XC2S50-5TQG144I FPGA предлагает около 50 000 системных ворот.Это позволяет поддерживать сложные цифровые конструкции и приложения, требующие значительного объема возможностей логической обработки.

• Логические ячейки: Это устройство включает в себя 1728 логических ячеек, которые облегчают реализацию сложных логических конфигураций и создание различных цифровых функций в FPGA.

• Конфигурируемые логические блоки (CLBS): Он имеет 384 настраиваемые логические блоки (CLBS), обеспечивая основу для логики FPGA.Эти блоки могут быть запрограммированы и перенастроены в соответствии с конкретными требованиями к конструкции, повышая общую универсальность устройства.

• БАРАН: FPGA оснащен 32 768 битами внутренней оперативной памяти, предлагая эффективные возможности хранения данных и поиска данных для задач, включающих манипулирование данными и временное хранение данных.

• Булавки ввода/вывода: С 92 выводами ввода/вывода XC2S50-5TQG144I обеспечивает достаточное внешнее соединение, позволяя ему взаимодействовать с другими устройствами и компонентами в системе для комплексной интеграции системы.

• Рабочее напряжение: Устройство работает при номинальном напряжении 2,5 В, с приемлемым диапазоном от 2,375 В до 2,625 В.Этот диапазон напряжения помогает обеспечить стабильную работу и надежную производительность в различных электрических условиях.

• Температурная диапазон: XC2S50-5TQG144I предназначен для эффективной работы в широком температурном диапазоне, от -40 ° C до +100 ° C, что делает его подходящим для развертывания в средах с сложными тепловыми условиями.

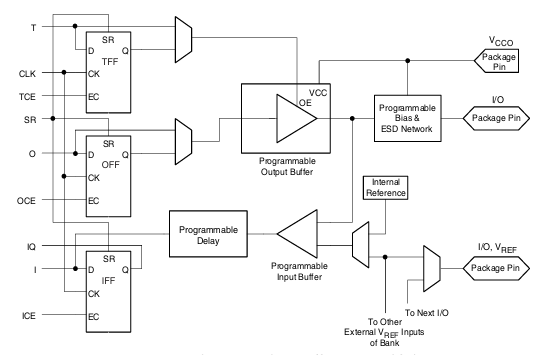

XC2S50-5TQG144I-диаграмма

Диаграмма показывает, как сигналы въезжают и выходят из XC2S50-5TQG144I FPGAПолемОн объясняет, как чип обрабатывает входные и выходные сигналы для связи с другими компонентами.На выходная сторона , сигналы поставляются изнутри FPGA и проходят через единицы хранения, называемые шлепанцами.Эти шлепанцы содержат данные и убедились, что сигналы меняются в нужное время.Затем сигналы проходят через программируемый выходной буфер, который регулирует, насколько силен сигнал, и контролирует, насколько быстро он меняется.Существует также переключатель (управление OE), который решает, должен ли выходной вывод или оставаться в стороне.Схема защиты предотвращает повреждение статического электричества, прежде чем сигнал достигнет контактов ввода/вывода, которые подключаются к другим устройствам.На входная сторона, сигналы извне проводят через программируемый входной буфер, который обрабатывает их перед отправкой в FPGA.Программируемая блока задержки помогает регулировать время сигнала, чтобы все оставалось синхронизированным.FPGA также может использовать внутреннее эталонное напряжение (VREF) для соответствия различным уровням напряжения, что облегчает работу с различными типами цепей.Некоторые выводы ввода/вывода имеют эту ссылку на напряжение, чтобы сохранить стабильные сигналы.Эта конструкция помогает FPGA эффективно управлять сигналами, обеспечивая правильное время, защиту и совместимость с различными электронными компонентами.

XC2S50-5TQG144I Спецификации

|

Тип |

Параметр |

|

Производитель |

AMD XILINX |

|

Ряд |

Spartan®-II |

|

Упаковка |

Поднос |

|

Статус частично |

Устаревший |

|

Количество лабораторий/CLBS |

384 |

|

Количество логических элементов/ячеек |

1728 |

|

Всего битов RAM |

32 768 |

|

Номер в/вывода |

92 |

|

Количество ворот |

50 000 |

|

Напряжение - поставка |

2,375 В ~ 2,625 В. |

|

Монтажный тип |

Поверхностное крепление |

|

Рабочая температура |

-40 ° C ~ 100 ° C (TJ) |

|

Пакет / корпус |

144-LQFP |

|

Пакет устройства поставщика |

144-TQFP (20x20) |

|

Базовый номер продукта |

XC2S50 |

Приложения XC2S50-5TQG144I

Встроенные системы

В встроенных системах XC2S50-5TQG144I предоставляет необходимую логику для приложений на основе микроконтроллеров.Он широко используется в автомобильной электронике, портативных устройствах и мелкой робототехнике для повышения функциональности и отзывчивости.

Обработка сигнала

FPGA превосходит задачи обработки сигналов, где требуется ее способность выполнять параллельную обработку.Он идеально подходит для обработки аудио и видео, телекоммуникаций и анализа данных, предоставляя мощность для обработки сложных алгоритмов и высокоскоростных потоков данных.

Промышленные системы управления

Системы промышленного управления извлекают выгоду из этой надежности и программируемости этой FPGA, что делает его подходящим для таких приложений, как управление процессами, автоматизация машины и мониторинг системы.Его надежность обеспечивает постоянную производительность в средах, требующих точности и операционной стабильности.

Системы связи

В системах связи XC2S50-5TQG144I помогает управлять передачей и приемом данных, поддержкой, такими как модуляция сигнала и демодуляция, преобразование протокола и сетевой маршрутизацию.Его адаптируемость является ключом к развитию телекоммуникационных инфраструктур и новых беспроводных технологий.

Прототипирование и развитие

FPGA также широко используется для прототипа цифровых цепей.Многие используют его для тестирования и уточнения своих идей до окончательного производства, особенно в сложных проектах по проектированию ASIC и пользователя.Эта возможность снижает время развития и затраты, ускоряя путь от концепции к рынку.

XC2S50-5TQG144I Аналогичные части

XC2S50-5TQG144I Преимущества

Экономическая эффективность

XC2S50-5TQG144I выделяется благодаря своей доступности, обеспечивая больше функций на доллар, чем многие конкурирующие FPGA.Эта экономическая эффективность достигается за счет передовой технологии процессов и эффективной архитектуры, что позволяет более широко развертываться на рынках, чувствительных к затратам.

Высокопроизводительный ввод-вывод и упаковка

Эта FPGA поддерживает широкий спектр стандартов ввода/вывода и доступен в различных вариантах рентабельной упаковки.Эти функции гарантируют, что устройство может быть интегрировано в несколько приложений, не жертвуя производительностью, что делает его идеальным как для высококлассных, так и для рынков, управляемых объемом, где универсальность интерфейса и физические ограничения являются факторами.

Функции системного уровня

Оснащенная функциями управления памятью, такими как распределенная ОЗУ и настраиваемая блочная оперативная память, XC2S50-5TQG144I повышает эффективность обработки данных.Эти функции облегчают сложные задачи хранения данных и обработки, повышая общую производительность и масштабируемость системы.

Перепрограммирование

Перепрограммируемость XC2S50-5TQG144I позволяет неограниченные модификации своей конфигурации, что полезно на этапе разработки.Эта гибкость позволяет уточнить проекты с помощью итеративных обновлений без дополнительных затрат на оборудование, способствовать инновациям и сокращения времени до конечного продукта.

XC2S50-5TQG144I Шаги программирования

Программирование FPGA XC2S50-5TQG144I из серии AMD Xilinx Spartan-II включает в себя структурированную серию шагов, предназначенных для эффективного перевода цифровой конструкции в функциональную конфигурацию FPGA.Вот интегрированное и подробное руководство, которое поможет вам в процессе программирования:

1. Дизайн

Начните с фазы входа в дизайн, где вы создаете свою цифровую логику, используя язык оборудования описания (HDL), такой как VHDL или Verilog.Этот начальный шаг включает в себя детализацию функциональности и логики, которые вы хотите реализовать в FPGA.Требуется, чтобы ваш дизайн был точным и точно представлял предполагаемые операции для обеспечения успешного синтеза и реализации.

2. Синтез

На этапе синтеза используйте инструмент синтеза для преобразования вашего кода HDL в список сети.Слист сети-это разбивка вашего дизайна в формат, который включает в себя различные взаимосвязанные логические элементы, такие как ворота и шлепанцы.Этот процесс переводит ваш теоретический дизайн в практическую чертеж, который FPGA может понять и реализовать.

3. Реализация

Реализация включает в себя несколько подборов: картирование, размещение и маршрутизация.Картирование присваивает элементы вашего списка сети определенным логическим блокам в FPGA.Размещение определяет физические местоположения этих блоков на чипе FPGA, чтобы оптимизировать производительность и использование ресурсов.Маршрутизация соединяет эти блоки с помощью программируемых ресурсов FPGA Interconnect.Этот этап гарантирует, что дизайн соответствует всем физическим и производительным ограничениям.

4. Определение ограничения

В процессе проектирования необходимы определение ограничений.Ограничения направляют инструменты реализации, указав такие требования, как время (как быстро FPGA должна работать), и назначения PIN (которые выводы на FPGA будут подключаться к различным частям вашего оборудования).Они сформулированы в файле пользовательских ограничений (UCF), который помогает в тонкой настройке дизайна для соответствия конкретным операционным стандартам.

5. Bitstream Generation

Как только ваш дизайн успешно пройдет на этапе реализации, следующим шагом является создание файла Bitstream.Этот файл содержит все данные конфигурации, необходимые FPGA для выполнения проекта.Bitstream - это конечный выход процесса программирования, представляющий полное запрограммированное состояние FPGA.

6. Программирование устройства

Последним шагом является загрузка бит-стрижки в FPGA XC2S50-5TQG144I, что можно сделать с использованием различных режимов конфигурации в зависимости от вашей настройки.В Мастер -серийный режим, FPGA Автономно считывает данные конфигурации из прикрепленного последовательного PROM (программируемая память только для чтения). Рабский серийный режим Позволяет внешнему главному устройству, такому как микроконтроллер, последовательно подавать данные конфигурации FPGA. Рабский параллельный режим Включает высокоскоростное программирование путем предоставления данных конфигурации параллельно от внешнего главного устройства.Наконец, Режим граничного сканирования (JTAG) Использует интерфейс JTAG как для программирования, так и для тестирования, что делает его полезным во время разработки для итеративной отладки и проверки.

XC2S50-5TQG144I Размеры упаковки

А XC2S50-5TQG144I Полевой программируемый массив ворот (FPGA) из семьи Spartan-II в Xilinx, размещенном в 144-контактный тонкий Quad Flat Pack (TQFP) пакетПолемЭтот пакет измеряет 20 мм х 20 ммПолем

XC2S50-5TQG144I Производитель

XC2S50-5TQG144I-это FPGA из семейства Спартанского II, изготовленного AMD Xilinx.Xilinx, теперь часть Амд, является ведущей полупроводниковой компанией, специализирующейся на FPGA, адаптивных SOC и других программируемых логических устройствах.XC2S50-5TQG144I был первоначально разработан в серии Xilinx Spartan-II, предлагая 50 000 системных ворот и 1728 логических ячеек, предназначенных для высокоэффективных, но экономически эффективных применений.Благодаря приобретению Xilinx от AMD, компания продолжает поддерживать устаревшие продукты, такие как серия Spartan-II, в то же время продвигая новые архитектуры FPGA.Тем не менее, XC2S50-5TQG144I является FPGA более старого поколения и может столкнуться с возможным устаревшим, поскольку AMD Xilinx сдвигает фокус на более продвинутые семейства FPGA.

Заключение

FPGA XC2S50-5TQG144I-это экономически эффективный и перепрограммируемый чип, который предлагает отличную производительность и гибкость.Он широко используется в встроенных системах, промышленных машинах и сети связи из-за его высокоскоростной обработки и сильных вариантов подключения.Эта FPGA помогает протестировать и разрабатывать новые идеи до окончательного производства запрограммировать и обновлять, эта FPGA помогает проверить и разрабатывать новые идеи.Хотя доступны более новые FPGA, эта модель остается надежным выбором для проектов, которые требуют надежного и доступного решения FPGA.Это руководство содержит четкий и простой обзор функций, использования и процесса программирования FPGA, что делает его ценным ресурсом для всех.

О нас

ALLELCO LIMITED

Прочитайте больше

Быстрое запрос

Пожалуйста, отправьте запрос, мы ответим немедленно.

Часто задаваемые вопросы [FAQ]

1. Могу ли я использовать XC2S50-5TQG144I для высокоскоростных приложений?

XC2S50-5TQG144I поддерживает скорость до 200 МГц, что делает его подходящим для большинства встроенных и промышленных применений.Однако, если ваш проект требуют высокоскоростных интерфейсов, таких как PCIe или DDR Memory, вам может потребоваться более продвинутая FPGA, такая как серия Spartan-6 или Artix-7.

2. Как XC2S50-5TQG144I по сравнению с более новым Spartan-3 или Spartan-6 FPGAS?

В то время как новые FPGA, такие как Spartan-3 или Spartan-6, предлагают повышенную производительность, более высокую логическую плотность и дополнительные функции, XC2S50-5TQG144i остается предпочтительным выбором для чувствительных к стоимости проектов с умеренной сложностью.Если вам требуется устаревшая совместимость или стабильная цепочка поставок, XC2S50-5TQG144I является отличным вариантом.

3. Какие инструменты программирования совместимы с FPGA XC2S50-5TQG144I?

XC2S50-5TQG144I запрограммирован с использованием Xilinx ISE (интегрированная программная среда).В то время как новые инструменты Xilinx, такие как Vivado, не поддерживают семейство Спартан-II, ISE предоставляет все необходимые проекты, синтез и функциональные возможности программирования для этой FPGA.

4. Могу ли я мигрировать существующий спартанский дизайн в более новую FPGA?

Да, но это требует модификаций.Более новые семейства Spartan-3 и Spartan-6 используют различную архитектуру, уровни напряжения и методы конфигурации.Если вы рассматриваете миграцию, мы можем помочь в выборе подходящих альтернатив и минимизации изменений дизайна.

5. Поддерживает ли XC2S50-5TQG144I программирование JTAG?

A: Да, FPGA поддерживает программирование пограничного сканирования JTAG (IEEE 1149.1), которое позволяет легко отлаживать и конфигурации с использованием стандартного интерфейса JTAG.Это полезно как для начального программирования, так и для реконфигурации без внешней памяти.

XC4013XL-3PQ240C FPGA: Альтернативы, спецификации, приложения и таблицы данных

на 2025/03/18

Усилители мощности РЧ: как они работают, какой тип более эффективен

на 2025/03/18

Популярные посты

-

Комплексный набор инструкций: как они изменили вычисления?

на 8000/04/18 147760

-

Поспинка и функции USB-C

на 2000/04/18 111969

-

Использование примитивах Unified моделирования Xilinx: комплексное руководство по проектированию и моделированию FPGA

на 1600/04/18 111351

-

Напряжения источника питания в электронике: значение VCC, VDD, VEE, VSS и GND

на 0400/04/18 83733

-

Руководство по разъему RJ45: расписка, проводка, типы кабелей и использование

на 1970/01/1 79520

-

Конечное руководство по цветовым кодам проволоки в современных электрических системах

То, как наши электрические системы используют цвета, не только для внешнего вида.Каждый цвет провода теперь указывает на определенную функцию, что облегчает правильную идентификацию и обработку эле...на 1970/01/1 66930

-

Руководство по очистке клапана: функция, симптомы, тестирование и замена для оптимальной производительности двигателя

Клапан чистки является ключевой частью системы автомобиля, которая помогает поддерживать воздух в чистоте, управляя топливными парами, прежде чем они смогут сбежать в атмосферу.Это не только помога...на 1970/01/1 63080

-

Качество (Q) Фактор: уравнения и приложения

Коэффициент качества, или «Q», важен при проверке того, насколько хорошо индукторы и резонаторы работают в электронных системах, которые используют радиочастотные (RF).«Q» измеряет, насколько хорош...на 1970/01/1 63024

-

Достижение пиковой производительности с максимальной теоремой передачи мощности

Теорема максимальной передачи мощности объясняет, как энергия из источника, такого как батарея или генератор, течет к подключенной нагрузке.Он показывает точное условие, где нагрузка получает наибо...на 1970/01/1 54090

-

Спецификации батареи A23 и совместимость

Аккумулятор A23 представляет собой небольшую батарею в форме цилиндров с высоким напряжением.Также называется 23a, 23ae или Mn21, он работает на 12 вольт и намного выше, чем батареи AA или...на 1970/01/1 52163